FPGA编译仿真的算力密码:从RTL代码到比特流的硬件加速之道

时间:2026-03-10 22:36:13

来源:UltraLAB图形工作站方案网站

人气:83

作者:管理员

在数字逻辑设计的前沿阵地,无论是开发5G基带处理单元、人工智能加速卡,还是航天级抗辐照芯片,FPGA工程师都在与时间赛跑。一个看似简单的代码修改,可能触发数小时的编译连锁反应;一次完整的时序收敛,往往需要经历几十轮迭代优化。当芯片规模从万门级跃升至亿门级,当单器件集成AI引擎、ARM核、高速收发器成为常态,FPGA编译仿真已不再是简单的"软件运行",而是对工作站硬件架构的极限压榨。

本文将深度拆解Xilinx Vivado、Intel Quartus Prime、Lattice Diamond等主流工具链的计算机理,揭示不同开发阶段对CPU、内存、存储的差异化需求,并为科研团队提供从原型验证到量产前的硬件选型黄金法则。

一、FPGA开发全链路:编译仿真究竟在算什么?

FPGA开发不是单一的"编译"动作,而是一个多阶段、异构化、强依赖的复杂工程流程。理解每个阶段的计算本质,是配置硬件的前提。

1.1 综合阶段(Synthesis)——逻辑炼金术

工作内容:将RTL(Verilog/VHDL/SystemVerilog)转化为门级网表,进行逻辑优化、资源共享、技术映射。 计算特征:

-

算法核心:图遍历、布尔满足性(SAT)求解、启发式优化算法

-

CPU需求:极度依赖单核性能,主频每提升1GHz,综合时间缩短15-20%

-

内存模式:随机读写频繁,需要大容量L3缓存(建议64MB+)降低延迟

-

典型耗时:中型设计(100K LUTs)约30-60分钟,大型设计(500K+ LUTs)可达3-8小时

1.2 布局布线(Place & Route)——几何博弈场

工作内容:物理布局(决定逻辑单元在芯片上的物理位置)与布线(连接信号路径),满足时序约束(Setup/Hold Time)。 计算特征:

-

算法核心:模拟退火、遗传算法、路径搜索(A*算法)、时序分析迭代

-

并行特性:Xilinx Vivado支持多线程布局(

-jobs参数),但布线阶段并行度受限,通常4-8线程最优 -

内存杀手:超大规模FPGA(如Virtex UltraScale+ VU19P)布线阶段可消耗200GB-400GB物理内存

-

IO特征:频繁读取物理库文件(.xdc约束、器件模型),需要高速SSD降低卡顿

1.3 静态时序分析(STA)——纳秒级审判

工作内容:验证所有信号路径是否满足时序约束,建立/保持时间余量(Slack)分析,生成时序报告。 计算特征:

-

计算类型:图最短路径算法(Bellman-Ford改进型),依赖内存带宽

-

并行能力:可完全并行化,线程数与CPU核心数正相关

-

内存占用:与网表规模成正比,通常需布局布线阶段内存的30-50%

1.4 功能仿真(Functional Simulation)——逻辑预言家

工作内容:通过ModelSim、VCS、XSIM等工具验证RTL功能正确性,运行Testbench激励。 计算特征:

-

行为级仿真:单核高频敏感,事件驱动调度(Event-driven)机制

-

门级仿真:计算密集型,需处理大量延迟模型和开关活动

-

波形Dump:Dump波形文件(.wlf/.fsdb)时产生巨大IO压力,单个文件可达10GB-100GB

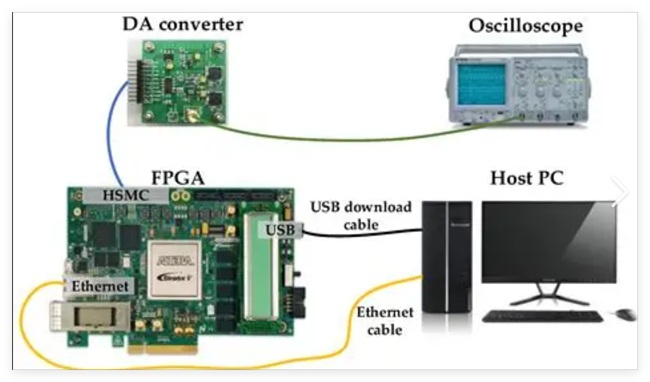

1.5 硬件仿真加速(Emulation/Prototyping)——原型验证

工作内容:使用Synopsys ZeBu、Cadence Palladium或自研FPGA集群进行软硬件协同仿真。 计算特征:

-

编译分割:将大型ASIC设计分割到多块FPGA,需解决引脚分配、时域分割(TDM)

-

内存需求:极端场景下,编译环境需要1TB+内存处理千万门级网表分割

二、计算规模分级:你的设计属于哪一级?

FPGA编译的硬件需求与目标器件规模呈指数级关系。我们按Xilinx/Intel主流产品线的逻辑资源(LUTs/FFs)将计算负载分为四级:

Level 1:轻量级(Artix-7、Cyclone V、ECP5)

-

资源规模:10K-50K LUTs

-

内存需求:16GB-32GB(基础编译),64GB(多项目并行)

-

CPU需求:8核16线程,主频3.5GHz+

-

典型应用:教学实验、工业控制、通信协议栈验证

-

编译耗时:综合5-15分钟,布局布线10-30分钟

Level 2:中规模(Kintex-7、Arria 10、Zynq-7000)

-

资源规模:100K-300K LUTs

-

内存需求:64GB-128GB(关键路径:布局布线峰值占用80GB+)

-

CPU需求:16核32线程,基频4.0GHz+

-

典型应用:软件定义无线电(SDR)、机器视觉处理、边缘AI推理

-

编译耗时:综合30-60分钟,布局布线2-6小时(时序收敛困难时可达12小时)

Level 3:大规模(Virtex UltraScale+、Stratix 10、Zynq UltraScale+ MPSoC)

-

资源规模:500K-1.5M LUTs,集成ARM Cortex-A53/A72、GPU、AI引擎

-

内存需求:256GB-512GB(VU19P全芯片编译实测占用380GB内存)

-

CPU需求:32核64线程以上,支持AVX-512指令集加速浮点运算

-

存储需求:NVMe SSD 4TB+(编译缓存+多版本网表存储),读写速度3GB/s+

-

典型应用:5G基站基带处理、数据中心加速卡(SmartNIC)、自动驾驶原型验证

-

编译耗时:综合2-4小时,布局布线8-24小时(迭代收敛需数天)

Level 4:超大规模/多FPGA原型(Versal ACAP、Stratix 10 MX、多板卡集群)

-

资源规模:2M+ LUTs,或4-32块FPGA互联原型系统

-

内存需求:512GB-2TB(Synopsys Protocompiler分割算法内存饥渴型)

-

CPU需求:双路服务器级处理器(如AMD EPYC 9004系列、Intel Xeon Scalable),64核128线程+

-

网络需求:100Gbps RDMA网络(多机编译场景)

-

典型应用:AI训练芯片原型、CPU/GPU仿真、超大规模ASIC验证

三、硬件配置黄金法则:别让工具链"饿着"

基于上述计算特征,我们为科研团队与工程实验室制定以下配置策略:

3.1 CPU选型:单核高频与多核并重的平衡术

核心矛盾:综合与布局布线早期阶段是"单核游戏",而STA、DRC检查、多策略运行(Multi-Corner/Multi-Mode)可充分利用多核。

推荐方案:

-

桌面工作站级:AMD Ryzen Threadripper PRO 7975WX(32核64线程,基频4.0GHz,Max Boost 5.3GHz)

-

优势:sTR5平台支持8通道DDR5,128条PCIe 5.0通道,兼顾单核爆发与多核并行

-

竞品对比:Intel Xeon W-3475X(28核,4.8GHz Turbo)单核性能稍弱,但AVX-512对部分HLS综合有优化

-

-

服务器级:AMD EPYC 9334(32核,3.9GHz)或Intel Xeon Gold 6448Y(32核,4.1GHz Turbo)

-

适用场景:团队共享编译服务器,需支持多用户同时提交作业

-

避坑指南:

-

避免使用"高频低核"游戏CPU(如i9-14900K),虽然单核快,但64GB内存上限无法支持大型FPGA编译

-

避免"多核低频"服务器CPU(如某些ARM服务器),Vivado/Qtus对ARM架构支持有限且单核性能不足导致综合缓慢

3.2 内存配置:FPGA编译的"阿喀琉斯之踵"

这是最容易被低估的硬件指标。

配置策略:

-

最小可行配置:128GB DDR5-4800 ECC(适用于Level 1-2)

-

科研级标配:256GB DDR5-4800 ECC RDIMM(Level 3入门,支持VU9P/VU13P级芯片)

-

极限配置:512GB-1TB DDR5(Level 4,Versal VCK190全系统编译)

关键技术细节:

-

通道数:务必插满8通道(双路CPU为16通道),内存带宽直接影响布线算法的图遍历速度

-

ECC必须:FPGA编译动辄数小时,内存错误导致编译崩溃的成本极高

-

预留策略:实际占用内存的1.5倍余量。例如,若设计峰值占用200GB,应配置256GB而非刚好200GB,避免操作系统杀进程(OOM Killer)

3.3 存储系统:IO瓶颈的隐形杀手

FPGA工具链产生海量小文件(.dcp检查点、.log日志、.rpt报告),且频繁随机读写。

分级存储方案:

-

L1缓存层:2TB NVMe Gen4 SSD(如Samsung PM9A3、Intel P5510)

-

用途:操作系统+工具链安装,Vivado/Quartus安装包本身就有50GB+

-

要求:随机读写IOPS 500K+,顺序读速7000MB/s+

-

-

L2工作层:4TB-8TB NVMe Gen4 SSD(企业级U.2接口,如Intel P5800X Optane或KCD81PJE)

-

用途:项目工作目录、编译缓存(Vivado's

.cache目录可设置在此) -

关键: Optane SSD的超高耐久度(DWPD 100+)适合频繁写入的编译缓存

-

-

L3归档层:NAS或本地SATA SSD(16TB+)

-

用途:历史版本bitstream、仿真波形文件、长期归档

-

高级技巧:

-

使用

mklink或mount --bind将Vivado的*.cache目录映射到独立高速SSD -

启用RAM Disk(内存盘)存放临时文件:对128GB+内存机器,可分配32GB作为/tmp目录,极大加速综合阶段的临时文件操作

3.4 显卡与显示:被忽视的效率工具

虽然FPGA编译不依赖GPU计算,但高端显卡对调试效率至关重要:

-

4K多屏支持:时序报告、原理图查看、波形分析需要巨大屏幕空间,建议配置NVIDIA T1000或RTX A2000(支持4屏4K输出)

-

编码加速:录制调试过程、生成教程视频时,NVENC编码器可减轻CPU负担

3.5 网络与集群:团队作战的利器

对于高校实验室或企业研发部,编译任务队列化是常态:

-

作业调度系统:配置SLURM或LSF,将编译任务分发到多台工作站

-

高速互联:100Gbps InfiniBand或25Gbps以太网,快速传输大型设计文件(未压缩的FPGA项目常达50GB+)

-

版本控制服务器:Git LFS管理二进制IP核,需高速SSD支持大文件检出

四、UltraLAB FPGA工作站配置矩阵

针对前述四级应用场景,我们提供可横向扩展的硬件方案:

方案A:科研入门型(UltraLAB AR350)

定位:研究生个人工作站,中小规模FPGA开发 配置:

-

CPU:AMD Ryzen 9 7950X(16核32线程,5.7GHz加速频率)

-

内存:128GB DDR5-5200 ECC(4×32GB,双通道,预留4槽升级)

-

存储:2TB Gen4 NVMe(系统)+ 4TB Gen4 NVMe(项目盘)

-

显卡:NVIDIA T1000 8GB(4屏输出)

-

特色:静音设计(满载<40dB),适合放置办公室

方案B:专业开发型(UltraLAB GR450M)

定位:博士生/工程师主力机型,支持Virtex-7/Virtex UltraScale+ 配置:

-

CPU:AMD Threadripper PRO 7975WX(32核64线程,8通道内存)

-

内存:256GB DDR5-4800 ECC RDIMM(8×32GB,满通道)

-

存储:2TB Gen4 NVMe(系统)+ 8TB U.2 NVMe(Intel P5800X级编译缓存)

-

网络:双万兆以太网(10GbE),支持iSCSI高速存储扩展

-

扩展:预留4个U.2硬盘位,支持RAID 0/1/10阵列

方案C:企业级集群节点(UltraLAB EA660)

定位:多FPGA原型验证、大型团队共享编译农场 配置:

-

CPU:双路 AMD EPYC 9334(64核128线程,单路基频3.9GHz)

-

内存:512GB DDR5-4800 ECC RDIMM(16×32GB,16通道)

-

存储:RAID 5阵列(4×4TB NVMe),读取速度达21GB/s

-

网络:100Gbps InfiniBand EDR(连接存储服务器与其他计算节点)

-

系统:预装CentOS/Ubuntu Server + SLURM作业调度系统

五、实战优化:让硬件性能榨干到最后一滴

即使配备顶级硬件,不当的设置仍会导致编译缓慢:

-

Vivado多线程设置:tcl

set_param general.maxThreads 16 # 根据CPU核心数调整,通常物理核心数×2注意:布线阶段超过8线程收益递减,但综合阶段可满载。 -

增量编译策略: 使用

write_checkpoint和read_checkpoint保存布局布线结果,修改RTL后仅重新编译受影响模块,可节省80%时间。这要求高速NVMe存储以快速读写.dcp文件(大型检查点可达10GB+)。 -

内存分页优化: 在Linux系统上,设置

vm.swappiness=10减少交换分区使用,避免编译大项目时因内存颠簸(Thrashing)导致性能暴跌。 -

分布式编译: 对于支持DSE(Design Space Exploration)的策略遍历,使用多机并行跑不同实现策略,快速收敛最优时序。

结语:算力即生产力,硬件即竞争力

在FPGA开发领域,"等待编译"是隐性成本最高的环节。一个需要迭代50次的设计,若每次编译节省2小时,整个项目周期可缩短数周。对于争取发论文的研究生,这意味着赶上会议Deadline的可能;对于商业团队,这是抢占市场窗口期的关键。

UltraLAB深谙FPGA工具链的硬件饥渴特性,我们的工作站不是通用PC的简单升级,而是针对高主频、大内存、高IO三维需求定制的专用平台。从单台静音工作站到百节点编译集群,我们提供全生命周期的算力支持——让您的创造力不再受限于进度条的爬行速度。

UltraLAB 定制图形工作站

专注高端科研计算20年

咨询电话 400-7056-800

微信号 xasun001