尖端半导体设计、算法、软件工具,及工作站/服务器集群硬件配置推荐

尖端半导体设计(先进制程IC设计)通常涵盖从器件结构创新到完整SoC系统落地的全链条研究,涉及算法、EDA软件和硬件配置都有极高要求。

我给你分成四部分说明:研究方向 → 核心算法 → 软件工具 → 硬件配置建议。

1. 主要研究方向

- 器件与工艺级设计

- 新型晶体管结构(GAA-FET、CFET、纳米片等)

- 新材料(2D材料、SiGe、InGaAs、氧化物半导体等)

- 先进制程工艺优化(2nm、3nm、EUV光刻工艺等)

- 电路级设计

- 高速、高密度逻辑单元设计(标准单元库开发)

- 高性能模拟/混合信号电路(ADC/DAC、PLL、SerDes)

- 低功耗架构设计与优化

- 系统级SoC/Chiplet设计

- 异构集成(CPU+GPU+AI加速器+DSP)

- Chiplet互连(UCIe、BoW、AIB等)

- 片上网络(NoC)与功耗/时序优化

- 验证与后端优化

- 物理设计(布局布线、寄生提取、时序收敛)

- 功耗/温度/信号完整性分析

- 先进封装(2.5D/3D IC、Fan-out、CoWoS、InFO)

2. 涉及的核心算法

尖端半导体设计是一个高度依赖自动化设计工具(EDA)和复杂算法的领域。计算环节复杂,算法可分为以下几类:

|

环节 |

主要算法 |

计算特点 |

|

器件仿真(TCAD) |

有限元法(FEM)、有限差分法(FDM)、蒙特卡罗方法(MC)、量子输运算法(NEGF) |

高精度浮点计算(FP64),内存带宽和CPU浮点性能为瓶颈 |

|

逻辑综合与优化 |

布尔代数、图论(图划分、最小割)、布尔可满足性求解器(SAT/SMT)、约束优化 |

CPU多核可加速,但单核延迟仍重要 |

|

布局布线(P&R) |

A*、Dijkstra、启发式搜索、模拟退火、遗传算法、整数线性规划 |

高内存占用、并行度中等 |

|

时序分析(STA) |

拓扑遍历、静态路径分析、RC网络建模、延迟方程求解 |

I/O操作多、单线程计算多 |

|

功耗与热分析 |

数值积分、有限体积法(FVM)、矩阵稀疏求解 |

内存占用大,适合GPU加速部分环节 |

|

信号完整性与电磁仿真 |

FDTD、FEM、矩阵分解(LU、QR)、快速多极子法(FMM) |

需要高内存带宽和多节点并行 |

|

3D封装热应力分析 |

多物理场耦合(热-电-力),非线性有限元 |

高内存/多核CPU计算优先 |

3. 常用软件(EDA工具链)

EDA(Electronic Design Automation)工具是半导体设计的“大脑”,主要由三家公司主导:

|

设计阶段 |

主流软件 |

说明 |

|

器件级 |

Synopsys Sentaurus TCAD、Silvaco ATLAS、COMSOL Multiphysics |

模拟晶体管/器件物理特性 |

|

前端设计 |

Synopsys Design Compiler、Cadence Genus、Siemens Aprisa |

逻辑综合、RTL优化 |

|

功能验证 |

仿真验证 |

|

|

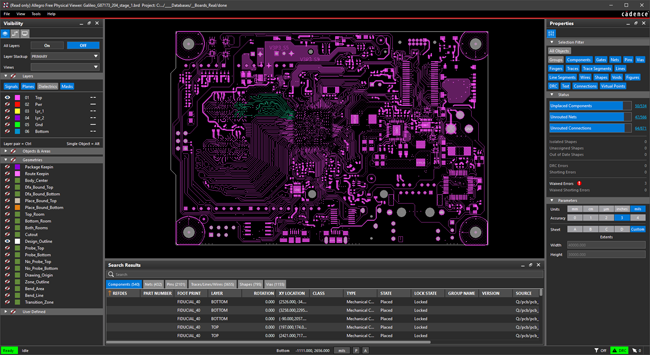

物理设计 |

Cadence Innovus、Synopsys IC Compiler II |

布局布线、时序收敛 |

|

寄生提取 |

Synopsys StarRC、Cadence Quantus |

提取RC参数 |

|

时序分析 |

Synopsys PrimeTime、Cadence Tempus |

静态时序分析 |

|

信号/功耗/热分析 |

Ansys RedHawk-SC、Cadence Voltus |

电源完整性、热分析 |

|

封装/3D集成 |

Cadence SiP、Ansys SIwave、Ansys Icepak |

封装与互连仿真 |

4. 硬件配置推荐

高端半导体设计平台通常分为设计工作站和集群服务器两类。

(1) 高端IC设计工作站

单机用,适合RTL开发、验证、小规模P&R,一个用于尖端半导体设计的工作站,其配置通常远超普通家用电脑,更接近于小型服务器。

- CPU:AMD Ryzen Threadripper 7970X(32核5GHz超频)

或 Intel Xeon w7-2495X(24核4.8GHz)

- 内存:512 GB~1TB DDR5 ECC(物理设计阶段内存需求极高)

- 存储:系统盘 4TB NVMe SSD(≥7GB/s);

数据盘 企业级 NVMe SSD 阵列(≥10TB,≥6GB/s)

- GPU:NVIDIA RTX 6000 Ada(部分EDA GUI/AI加速)

- 网络:10–25 GbE

- OS:RHEL / CentOS / Rocky Linux(与EDA工具兼容)

(2) EDA集群服务器

适合大规模并行仿真、时序分析、RC提取

- 计算节点:

- 并行加速:支持EDA多核并行(IC Compiler II、Innovus)

- 网络:100 Gbps InfiniBand(低延迟,方便分布式P&R、STA)

- 调度系统:Slurm / LSF

- 存储:90TB以上闪存阵列

史上最强大的--EDA/IC芯片/集成电路设计计算服务器存储集群配置方案

https://www.xasun.com/article/112/2799.html

科研团队计算利器2---自动化设计EDA计算平台配置推荐25v1

https://www.xasun.com/news/html/?2528.html

对于不同规模的半导体设计任务,可根据具体需求调整硬件配置,复杂任务建议采用多核并行计算和GPU加速相结合的方式,以提高整体计算效率。